Teaching Periods 03

Weightage % 02

1st Remote of world, In 1898, Nikola Tesla invented "teleautomation", which he demonstrated with a radio-controlled miniature boat, the first remote control device ever made. The remote control system contained a method for decoding Hertzian waves. This system would toggle actions based on different signals, functioning as an AND gate.

#### In this unit student should be able to:

- Explain signal levels employed in digital electronics or circuits are 'high' (for example, +5 volts) and 'low' (for example, 0 volts)

- Describe the 'high' and 'low' states are referred to as '1' and '0' for open and close circuit respectively

- Recall electronic symbols of the logic gates AND, OR, NOT, NOR, NAND, XOR

- Use logic gates (AND, OR, NOT, NOR, NAND, XOR, combinations) and their truth tables for 2, 3 and 4 inputs

- Identify the behavior of a 2 inputs AND gate and a 2 inputs OR gate with simple circuit using 2 switches, a lamp and a battery

#### **Introduction:**

Digital electronics is a branch of electronics that deals with the manipulation of digital signals, represented as binary digits (0s and 1s).

Unlike analog electronics, which uses continuous signals, digital electronics processes discrete signals, enabling precise control and storage of information. This field encompasses the design, analysis, and application of digital circuits and systems, forming the foundation for modern computing, communication, and information processing technologies.

#### 23.1 Digital signal levels:

In digital electronics, signal levels are represented in various ways. Here are common digital signal levels:

#### 1. Low Level (0):

- > This represents the binary digit 0.

- ➤ In terms of voltage, it is associated with a lower voltage level.

- ➤ Often referred to as "low" or "logic 0."

#### 2. **High Level (1):**

- > This represents the binary digit 1.

- In terms of voltage, it is associated with a higher voltage level

- Often referred to as "high" or "logic 1."

#### 3. Threshold Level:

- > The threshold level is the voltage level that separates low and high states.

- > Signals below this threshold are interpreted as 0, and signals above it are interpreted as 1.

- > The threshold level helps define the noise margin and ensure reliable signal interpretation.

#### 4. Logic Levels:

Depending on the technology and the system, different logic levels might be used.

#### 5. Swing or Voltage Range:

- ➤ The difference in voltage levels between low and high states is often referred to as the swing or voltage range. For example, voltage varies from -5V to +5V will have a swing or voltage range of 10V.

- > A larger voltage swing can enhance noise immunity and signal reliability.

#### 23.1.2 Understanding Digital Signal Levels:

In digital electronics, the 'high' and 'low' states are often symbolically represented as '1' and '0,' respectively. This binary notation helps describe the states of open and closed circuits.

Noise immunity is a measure of how well a logic circuit can withstand unwanted electrical signals or noise without reacting to them.

If we deal with mathematics, then the binary system, using 1 or 0, will be employed. If we are dealing with voltage in a circuit, then HIGH or LOW can be utilized.

- ➤ **High State ('1'):** When a digital signal is in a 'high' state, it is typically associated with a closed circuit or a voltage level close to the maximum specified value. The symbolic representation for this state is '1'. It signifies the 'on' or 'active' state in many digital systems.

- > Low State ('0'): Conversely, the 'low' state is linked to an open circuit or a voltage level close to the minimum specified value. It is symbolically represented as '0'. This state signifies the 'off' or 'inactive' state in digital systems.

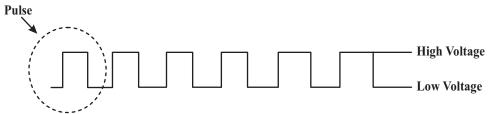

High and Low represent the **signal levels** in the circuit. Digital waveforms consist of voltage levels that are changing back and forth between the HIGH and LOW states. These can also be described as the one that is composed of series of pulses, or a pulse train as shown in Figure 23.1.

Figure 23. 1 Pulse showing High and Low states

These symbolic representations simplify the expression and interpretation of digital information, allowing for clear communication and logical operations within electronic circuits. The '1' and '0' states form the basic building blocks for encoding and processing binary data in digital systems. This binary representation forms the fundamental language of digital systems, allowing them to process and manipulate data efficiently.

The mathematics of binary system is different from ordinary mathematics. The special algebra representing binary system is known as Boolean Algebra.

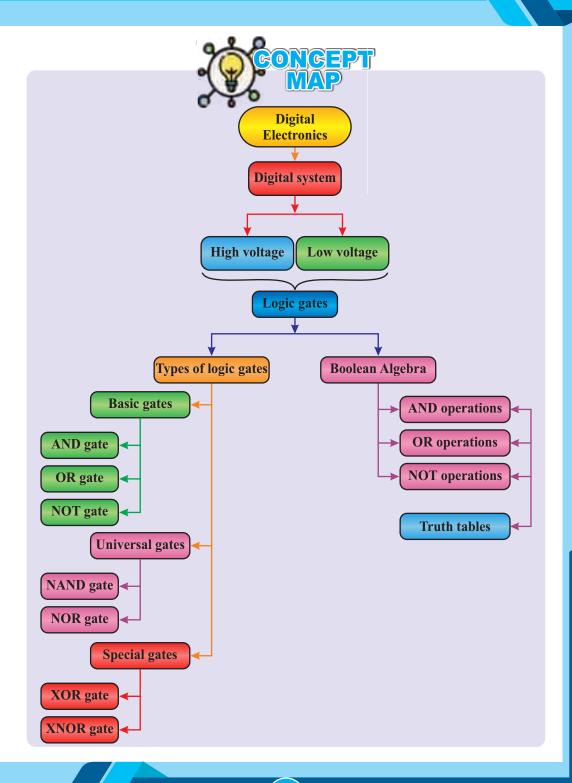

#### 23.2 Logic gates:

Logic gates are tiny electronic switches that enable decision-making in computers and other devices. They combine to perform logical operations, playing a crucial role in information processing.

#### 23.2.1 Types of Logic Gates:

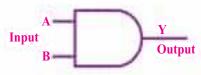

Logic gates are the basic components of the digital circuit with one output and more than one input. AND, OR, and NOT gates are the basic gates, while NAND and NOR are the universal gates. EX-OR and EX-NOR are the special gates.

Figure 23. 2 AND gate

#### 1. AND Gate:

The AND gate produces a 'high' output only when all its inputs are 'high.' In other words, the output of an AND gate attains state 1 if and only if all the inputs are in state 1.

The Boolean expression of AND gate and the Truth Table No:23.1 is given as for

Two-input Y = A.B

Three-input Y = A.B.C

Four input Y = A.B.C.D

|                                             | Truth Table No. 23.1: AND |   |   |                                      |   |   |   |   |   |   |   |

|---------------------------------------------|---------------------------|---|---|--------------------------------------|---|---|---|---|---|---|---|

| Two Input $Y = A.B$ Three Input $Y = A.B.C$ |                           |   |   | <b>Four Input Y</b> = <b>A.B.C.D</b> |   |   |   |   |   |   |   |

| A                                           | В                         | Y | A | В                                    | С | Y | A | В | С | D | Y |

| 0                                           | 0                         | 0 | 0 | 0                                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0                                           | 1                         | 0 | 0 | 0                                    | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1                                           | 0                         | 0 | 0 | 1                                    | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1                                           | 1                         | 1 | 0 | 1                                    | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

|                                             | 1 0 0 0                   |   |   |                                      |   |   |   | 1 | 0 | 0 | 0 |

|                                             |                           |   | 1 | 0                                    | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

|                                             |                           |   | 1 | 1                                    | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

|                                             |                           |   | 1 | 1                                    | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 0 | 0 | 0 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 0 | 0 | 1 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 0 | 1 | 0 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 0 | 1 | 1 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 1 | 0 | 0 | 0 |

|                                             |                           |   |   |                                      |   |   | 1 | 1 | 0 | 1 | 0 |

|                                             |                           |   |   |                                      |   | 1 | 1 | 1 | 0 | 0 |   |

|                                             |                           |   |   |                                      |   |   | 1 | 1 | 1 | 1 | 1 |

#### 2. OR Gate:

An OR gate generates a 'high' output if any of its inputs are 'high'. In other words, the output of an OR gate attains state 1 if one or more inputs attain state 1.

Figure 23. 3 OR gate

The Boolean expression of OR gate and the Truth Table No:23.2 is given as for

| 1. | Two-input   | Y = A + B         |

|----|-------------|-------------------|

| 2. | Three-input | Y = A + B + C     |

| 3. | Four input  | Y = A + B + C + D |

|                       | Truth Table No. 23.2: OR Gate |            |                  |   |          |            |   |                   |   |   |   |  |

|-----------------------|-------------------------------|------------|------------------|---|----------|------------|---|-------------------|---|---|---|--|

| Two Input Three Input |                               |            |                  |   |          | Four Input |   |                   |   |   |   |  |

| Y                     | =A+                           | ⊦ <b>B</b> | Y = A + B + C    |   |          |            |   | Y = A + B + C + D |   |   |   |  |

| A                     | В                             | Y          | $\boldsymbol{A}$ | В | <i>C</i> | Y          | A | В                 | С | D | Y |  |

| 0                     | 0                             | 0          | 0                | 0 | 0        | 0          | 0 | 0                 | 0 | 0 | 0 |  |

| 0                     | 1                             | 1          | 0                | 0 | 1        | 1          | 0 | 0                 | 0 | 1 | 1 |  |

| 1                     | 0                             | 1          | 0                | 1 | 0        | 1          | 0 | 0                 | 1 | 0 | 1 |  |

| 1                     | 1                             | 1          | 0                | 1 | 1        | 1          | 0 | 0                 | 1 | 1 | 1 |  |

|                       | 1 0 0 1                       |            |                  |   |          |            |   | 1                 | 0 | 0 | 1 |  |

|                       |                               |            | 1                | 0 | 1        | 1          | 0 | 1                 | 0 | 1 | 1 |  |

|                       |                               |            | 1                | 1 | 0        | 1          | 0 | 1                 | 1 | 0 | 1 |  |

|                       |                               |            | 1                | 1 | 1        | 1          | 0 | 1                 | 1 | 1 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 0                 | 0 | 0 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 0                 | 0 | 1 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 0                 | 1 | 0 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 0                 | 1 | 1 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 1                 | 0 | 0 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 1                 | 0 | 1 | 1 |  |

|                       |                               |            |                  |   |          |            | 1 | 1                 | 1 | 0 | 1 |  |

|                       |                               |            |                  |   |          | 1          | 1 | 1                 | 1 | 1 |   |  |

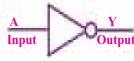

#### 3. NOT Gate:

It is used to perform the inversion operation in digital circuits, For example, the output of a NOT gate attains state 1 if and only if the input does not attain state 1.

The Boolean expression is:  $Y = \overline{A}$ It is read as Y equals NOT A. The truth table of NOT gate is given in table 23.3.

| Truth Table No. 23.3<br>NOT GATE |   |  |  |  |  |  |  |

|----------------------------------|---|--|--|--|--|--|--|

| A                                | Y |  |  |  |  |  |  |

| 0                                | 1 |  |  |  |  |  |  |

| 1                                | 0 |  |  |  |  |  |  |

Figure 23. 4: NOT gate

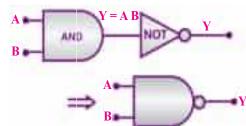

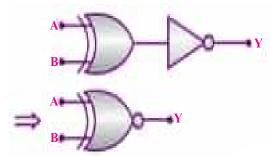

#### 4. **NAND Gate:**

Similarly, a NAND gate is an AND gate followed by a NOT gate, yielding the opposite output of an AND gate.

The Boolean expression of NAND gate

and the Truth Table No:23.4 is given as for

$Y = \overline{A.B}$ 1. Two-input

$Y = \overline{A.B.C}$ 2. Three\_input

$Y = \overline{A.B.C.D}$ 3. Four input

Figure 23.5 NAND GATE

| Truth Table No. 23.4: NAND Gate                                   |   |   |   |                                     |   |   |   |   |   |   |   |

|-------------------------------------------------------------------|---|---|---|-------------------------------------|---|---|---|---|---|---|---|

| Two Input $Y = \overline{A.B}$ Three Input $Y = \overline{A.B.C}$ |   |   |   | Four Input $Y = \overline{A.B.C.D}$ |   |   |   |   |   |   |   |

| A                                                                 | В | Y | A | В                                   | С | Y | A | В | C | D | Y |

| 0                                                                 | 0 | 1 | 0 | 0                                   | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0                                                                 | 1 | 1 | 0 | 0                                   | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1                                                                 | 0 | 1 | 0 | 1                                   | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1                                                                 | 1 | 0 | 0 | 1                                   | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

|                                                                   |   |   | 1 | 0                                   | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

|                                                                   |   |   | 1 | 0                                   | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

|                                                                   |   |   | 1 | 1                                   | 0 | 1 | 0 | 1 | 1 | 0 | 1 |

|                                                                   |   |   | 1 | 1                                   | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 0 | 0 | 0 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 0 | 0 | 1 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 0 | 1 | 0 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 0 | 1 | 1 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 1 | 0 | 0 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 1 | 0 | 1 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 1 | 1 | 0 | 1 |

|                                                                   |   |   |   |                                     |   |   | 1 | 1 | 1 | 1 | 0 |

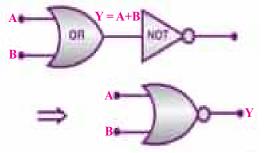

#### 5. NOR Gate:

A NOR gate is an OR gate followed by a NOT gate, providing the opposite result of an OR gate.

The Boolean expression of NOR gate and the Truth Table No:23.5 is given as for

1. Two-input  $Y = \overline{A + B}$

2. Three-input  $Y = \overline{A + B + C}$

3. Four input  $Y = \overline{A + B + C + D}$

Figure 23. 6

NOR gate and its equivalent diagram

| Truth Table No. 23.5: NOR Gate |                          |   |                  |                    |         |   |                                |   |   |   |   |

|--------------------------------|--------------------------|---|------------------|--------------------|---------|---|--------------------------------|---|---|---|---|

| Two Input Three Input          |                          |   |                  |                    |         |   | Four Input                     |   |   |   |   |

| Y                              | $=\overline{\mathbf{A}}$ | B |                  | $Y = \overline{A}$ | + B + C | 1 | $Y = \overline{A + B + C + D}$ |   |   |   |   |

| A                              | В                        | Y | $\boldsymbol{A}$ | В                  | C       | Y | A                              | В | С | D | Y |

| 0                              | 0                        | 1 | 0                | 0                  | 0       | 1 | 0                              | 0 | 0 | 0 | 1 |

| 0                              | 1                        | 0 | 0                | 0                  | 1       | 0 | 0                              | 0 | 0 | 1 | 0 |

| 1                              | 0                        | 0 | 0                | 1                  | 0       | 0 | 0                              | 0 | 1 | 0 | 0 |

| 1                              | 1                        | 0 | 0                | 1                  | 1       | 0 | 0                              | 0 | 1 | 1 | 0 |

|                                |                          |   | 1                | 0                  | 0       | 0 | 0                              | 1 | 0 | 0 | 0 |

| 1 0 1 0                        |                          |   |                  |                    |         | 0 | 1                              | 0 | 1 | 0 |   |

|                                |                          |   | 1                | 1                  | 0       | 0 | 0                              | 1 | 1 | 0 | 0 |

|                                |                          |   | 1                | 1                  | 1       | 0 | 0                              | 1 | 1 | 1 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 0 | 0 | 0 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 0 | 0 | 1 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 0 | 1 | 0 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 0 | 1 | 1 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 1 | 0 | 0 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 1 | 0 | 1 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 1 | 1 | 0 | 0 |

|                                |                          |   |                  |                    |         |   | 1                              | 1 | 1 | 1 | 0 |

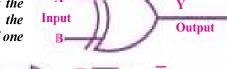

### 6. XOR Gate (Exclusive-OR Gate):

The XOR gate outputs a 'high' signal if the number of 'high' inputs is odd. In other words, the output of a two-input XOR gate attains state 1 if one adds only input and attains state 1.

The Boolean expression of XOR gate and Truth Table No:23.6 is given as for

1.

$$Y = A.\overline{B} + \overline{A}$$

2. Three-input

$$Y = A.\overline{B}.\overline{C} + \overline{A}.B.\overline{C} + \overline{A}.\overline{B}.C + A.B.C$$

3. Four input

$$Y = A \bigoplus B \bigoplus C \bigoplus D$$

Figure 23. 7 XOR gate and its equivalent diagram

| Truth Table No. 23.6: NOR Gate |                 |   |                  |                                                                          |                                            |   |                                               |   |   |   |   |

|--------------------------------|-----------------|---|------------------|--------------------------------------------------------------------------|--------------------------------------------|---|-----------------------------------------------|---|---|---|---|

|                                | vo Inp<br>= A.B |   |                  | $\mathbf{Y} = \mathbf{A}$ $\mathbf{A} \cdot \mathbf{B} \cdot \mathbf{C}$ | Input<br>. <u>B.C</u> +<br>+ A.B.(<br>.B.C |   | Four Input $Y = A \oplus B \oplus C \oplus D$ |   |   |   |   |

| A                              | В               | Y | $\boldsymbol{A}$ | В                                                                        | C                                          | Y | A                                             | В | С | D | Y |

| 0                              | 0               | 0 | 0                | 0                                                                        | 0                                          | 0 | 0                                             | 0 | 0 | 0 | 0 |

| 0                              | 1               | 1 | 0                | 0                                                                        | 1                                          | 1 | 0                                             | 0 | 0 | 1 | 1 |

| 1                              | 0               | 1 | 0                | 1                                                                        | 0                                          | 1 | 0                                             | 0 | 1 | 0 | 1 |

| 1                              | 1               | 0 | 0                | 1                                                                        | 1                                          | 0 | 0                                             | 0 | 1 | 1 | 0 |

| 1 0 0 1                        |                 |   |                  |                                                                          |                                            | 0 | 1                                             | 0 | 0 | 1 |   |

|                                |                 |   | 1                | 0                                                                        | 1                                          | 0 | 0                                             | 1 | 0 | 1 | 0 |

|                                |                 |   | 1                | 1                                                                        | 0                                          | 0 | 0                                             | 1 | 1 | 0 | 0 |

|                                |                 |   | 1                | 1                                                                        | 1                                          | 1 | 0                                             | 1 | 1 | 1 | 1 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 0 | 0 | 0 | 1 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 0 | 0 | 1 | 0 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 0 | 1 | 0 | 0 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 0 | 1 | 1 | 1 |

|                                |                 |   |                  |                                                                          |                                            | 1 | 1                                             | 0 | 0 | 0 |   |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 1 | 0 | 1 | 1 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 1 | 1 | 0 | 1 |

|                                |                 |   |                  |                                                                          |                                            |   | 1                                             | 1 | 1 | 1 | 0 |

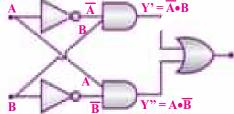

### 7. XNOR Gate (Exclusive-NOR Gate):

In the XNOR gate, the output is in state 1 when both inputs are the same, that is, both 0 or both 1.

The Boolean expression of XNOR gate and the Truth Table No:23.7 is given as for

1.

$$Y = ((A \bigoplus \overline{B})) = (A.B + \overline{A}.\overline{B})$$

2. Three-input

$$Y = ((\overline{A}). (\overline{B}) \overline{C}) + (A.B.C)$$

3. Four input

$$Y = (\overline{A}.(\overline{B}.)\overline{C}.\overline{D}) + (A.B.C.D)$$

Figure 23.8: XOR gate and its equivalent diagram

| $1 - (A \cdot (B \cdot) \cdot C \cdot B) + (A \cdot B \cdot C \cdot B)$ |                                 |   |                   |                                  |                                |                |   |   |   |   |   |  |

|-------------------------------------------------------------------------|---------------------------------|---|-------------------|----------------------------------|--------------------------------|----------------|---|---|---|---|---|--|

|                                                                         | Truth Table No. 23.7: XNOR Gate |   |                   |                                  |                                |                |   |   |   |   |   |  |

| Two Input $Y = ((A \oplus \overline{B}))$ Three Input $$                |                                 |   |                   |                                  |                                | Four Input     |   |   |   |   |   |  |

|                                                                         | $(A + \frac{1}{2})$             |   | $\mathbf{Y} = (0$ | <del>A</del> ). ( <del>B</del> ) | $\overline{\mathbf{C}}$ ) + (A | <b>A.B.C</b> ) |   |   |   |   |   |  |

| A                                                                       | В                               | Y | A                 | В                                | C                              | Y              | A | В | С | D | Y |  |

| 0                                                                       | 0                               | 1 | 0                 | 0                                | 0                              | 1              | 0 | 0 | 0 | 0 | 1 |  |

| 0                                                                       | 1                               | 0 | 0                 | 0                                | 1                              | 0              | 0 | 0 | 0 | 1 | 0 |  |

| 1                                                                       | 0                               | 0 | 0                 | 1                                | 0                              | 0              | 0 | 0 | 1 | 0 | 0 |  |

| 1                                                                       | 1                               | 1 | 0                 | 1                                | 1                              | 1              | 0 | 0 | 1 | 1 | 1 |  |

|                                                                         |                                 |   | 1                 | 0                                | 0                              | 0              | 0 | 1 | 0 | 0 | 0 |  |

|                                                                         | 1 0 1 1                         |   |                   |                                  |                                |                | 0 | 1 | 0 | 1 | 1 |  |

|                                                                         |                                 |   | 1                 | 1                                | 0                              | 1              | 0 | 1 | 1 | 0 | 0 |  |

|                                                                         |                                 |   | 1                 | 1                                | 1                              | 0              | 0 | 1 | 1 | 1 | 0 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 0 | 0 | 0 | 1 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 0 | 0 | 1 | 1 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 0 | 1 | 0 | 0 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 0 | 1 | 1 | 1 |  |

|                                                                         |                                 |   |                   |                                  |                                |                |   | 1 | 0 | 0 | 1 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 1 | 0 | 1 | 0 |  |

|                                                                         |                                 |   |                   |                                  |                                |                |   | 1 | 1 | 0 | 0 |  |

|                                                                         |                                 |   |                   |                                  |                                |                | 1 | 1 | 1 | 1 | 1 |  |

#### **Demonstration of Logic Gates in Simple Circuits:**

In this part, we are going to have some fun with simple circuits. By utilizing just 2 switches, a lamp and a battery, we explore the behaviors of a 2-input AND gate and a 2-input OR gate. These hands-on examples offer a concrete insight into how logic gates process signals and make logical decisions, forming the basis for more complex digital systems.

# DO YOU KNOW

The XNOR gate produces a high output (1) when an even number of its inputs are high (1).

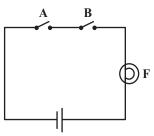

#### I. AND Gate Demonstration:

In this demonstration, we will use following components as shown in the circuit diagram:

- > 2 switches (Switch A and Switch B)

- > 1 lamp

- > 1 battery

The presented circuit exhibits two switches (A & B) and a bulb (F) arranged in series with a cell. According to basic circuit theory, the bulb illuminates only when a closed circuit permits the flow of current.

**Behavior:** The lamp will light up only when both Switch A and Switch B are in the ON position. If either or both switches are OFF, the lamp remains off.

However, in the context of digital electronics, we approach the analysis differently. Instead of focusing on the physical flow of current, we interpret the circuit as making decisions, determining whether the output represents logic 1(the bulb is lit) or logic 0 (bulb not lit). This decision is contingent upon the logical states of the inputs (i.e., the switches), where an open switch corresponds to logic 0 and a closed switch corresponds to logic 1.

The truth table and the equivalent combination of above circuit in logic gate is shown in figure 23.9.

Figure 23. 9(a)

AND gate circuit demonstration

Figure 23. 9(b) AND gate and its truth table

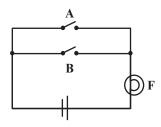

#### **II.** OR Gate Demonstration:

In this demonstration, we will use following components as shown in the circuit diagram:

- > 2 switches (Switch A and Switch B)

- > 1 lamp

- > 1 battery

Figure 23.10 shows a simple circuit which contains two switches in parallel.

**Behavior:** The lamp will light up if either or both Switch A and Switch B are in the ON position. The lamp remains off only when both switches are OFF.

Figure 23. 10(a) OR gate circuit demonstration

The truth table and the equivalent combination of above circuit in logic gate is shown in fig 23.10

In these circuits:

- For the AND gate, the output is HIGH (lamp on) only when both inputs are HIGH.

- For the OR gate, the output is HIGH (lamp on) when at least one input is HIGH.

These simple circuits demonstrate the basic principles of AND and OR gates, showcasing how they process signals based on logical operations.

Figure 23.10(b) OR gate and its truth table

- ✓ **Digital electronics** deals with digital signals represented by binary digits (0s and 1s).

- ✓ **Digital signals** use discrete voltage or current levels to represent information.

- ✓ **Common digital signal levels** include high level (logic 1), low level (logic 0), threshold level, and voltage swing.

- ✓ **Logic gates** are fundamental building blocks of digital circuits that perform logical operations on binary data.

- ✓ **Basic logic gates** include AND, OR, and NOT gates.

- ✓ NAND and NOR gates are universal gates that can be used to create any other logic gate

- ✓ **XOR and XNOR** gates are special logic gates used for specific operations.

- ✓ Logic gates can be implemented using transistors which act as electronic switches.

- ✓ **Simple circuits with switches and bulbs** can be used to demonstrate the behavior of AND OR gates.

## Section (A): Multiple Choice Questions (MCQs) Choose the correct answer:

| 1.  | The voltage level,                                                                       | typically associated with     | a 'low' state in digital ele | ectronic is:       |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------------|-------------------------------|------------------------------|--------------------|--|--|--|--|--|

|     | (a) -5 volts                                                                             | (b) 0 volts                   | (c) +5  volts                | (d) +10  volts     |  |  |  |  |  |

| 2.  | In binary represent                                                                      | ation, the correspond of '    | 0' in digital electronics i  | s:                 |  |  |  |  |  |

|     | (a) Low state                                                                            | (b) High state                | (c) Open circuit             | (d) Closed circuit |  |  |  |  |  |

| 3.  | The primary purpose of a truth table in digital electronics is to:                       |                               |                              |                    |  |  |  |  |  |

|     | (a) Determine inpu                                                                       | ıt voltage                    |                              |                    |  |  |  |  |  |

|     | (b) Measure circui                                                                       | t resistance                  |                              |                    |  |  |  |  |  |

|     | (c) Analyze output states based on input combinations                                    |                               |                              |                    |  |  |  |  |  |

|     | (d) Calculate circu                                                                      | it power                      |                              |                    |  |  |  |  |  |

| 4.  | . Which logic gate combination produces an output of '1' when at least one input is '1'? |                               |                              |                    |  |  |  |  |  |

|     | (a) AND                                                                                  | · /                           | ` /                          | (d) NOT            |  |  |  |  |  |

| 5.  | In a circuit with a                                                                      | 2-input OR gate, the statu    | is of the lamp if either sw  | vitch is closed    |  |  |  |  |  |

|     | (a) OFF                                                                                  | × /                           | ` /                          |                    |  |  |  |  |  |

| 6.  | The behavior of 2                                                                        | input AND gate, when be       | oth switches are closed, I   | Lamp is            |  |  |  |  |  |

|     | (a) OFF                                                                                  | (b) ON                        | (c) blinking                 | (d) flickering     |  |  |  |  |  |

| 7.  | In a 3-input OR ga                                                                       | te, if all inputs are '0'soth | e output will be:            |                    |  |  |  |  |  |

|     | (a) 1                                                                                    | (b) 0                         | × /                          | (d) Both A and B   |  |  |  |  |  |

| 8.  | If the input is '1', T                                                                   | The output of a NOT gate      | will be:                     |                    |  |  |  |  |  |

|     | (a) 1                                                                                    | (b) 0                         | < /                          |                    |  |  |  |  |  |

| 9.  | In a 2-input XOR                                                                         | gate, when both inputs ar     |                              | be                 |  |  |  |  |  |

|     | (a) 1                                                                                    | (b) 0                         | ( )                          | (d) Both A and B   |  |  |  |  |  |

| 10. |                                                                                          | n of logic gates is equiva    |                              |                    |  |  |  |  |  |

|     | (a) $AND + OR$                                                                           | (b) $NOT + NOR$               | (c) $OR + NAND$              | (d) $AND + NAND$   |  |  |  |  |  |

|     |                                                                                          |                               |                              |                    |  |  |  |  |  |

#### **Section (B):** CRQs (Short Answered Questions):

- 1. Explain the significance of signal levels in digital electronics and how they are represented in terms of voltage.

- 2. Describe the binary representation used in digital electronics. How is this representation related to the 'high' and 'low' states?

- 3. Choose any three logic gate symbols and explain their operations.

- 4. Create a combination of logic gates that mimics the behavior of an XOR gate.

#### **Section (C): ERQs (Long Answered Questions):**

- 1. Design a simple circuit using a 2-input AND gate, a switch, a lamp, and a battery. Explain how the circuit operates and the conditions under which the lamp will be illuminated.

- 2. Construct a truth table for a 3-input OR gate. Explain how the truth table represents the relationship between input combinations and the resulting output.